# SV3C DPRX MIPI D-PHY Analyzer

## Data Sheet

## Table of Contents

| Table of Contents1                                   |

|------------------------------------------------------|

| List of Figures                                      |

| List of Tables                                       |

| Introduction                                         |

| Overview4                                            |

| Key Benefits4                                        |

| Applications4                                        |

| Ordering Information5                                |

| Features                                             |

| Complete D-PHY Receiver Implementation6              |

| Protocol Analysis and Precision Time Stamps7         |

| Hardware CRC Checking and Packet Error Rate Testing8 |

| Advanced Trigger Modes8                              |

| Automation11                                         |

| Physical Description and Pinout12                    |

| Specifications                                       |

## List of Figures

| Figure 1    | SV3C receiver illustration showing automatic termination switches.                           | 6 |

|-------------|----------------------------------------------------------------------------------------------|---|

| Figure 2    | (a) Illustration of the DPRX as a terminating end-point receiver, or (b) while probing a     |   |

| complete    | D-PHY link                                                                                   | 6 |

| Figure 3    | Protocol analyzer views                                                                      | 7 |

| Figure 4    | Illustration of packet error rate testing                                                    | 8 |

| Figure 5    | Introspect ESP GUI for the SV3C DPRX. Top left: Components, shows CSI, DSI and PHY data      |   |

| acquisitio  | n methods. Top right: Properties, showing CSI Data capture. Bottom: test procedure ready to  |   |

| execute a   | CSI Data Capture, then PERT                                                                  | 9 |

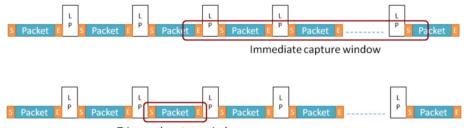

| Figure 6    | Illustration of multi-packet, per-lane PHY-level capture (Top), and triggered packet capture |   |

| (Bottom).   |                                                                                              | 9 |

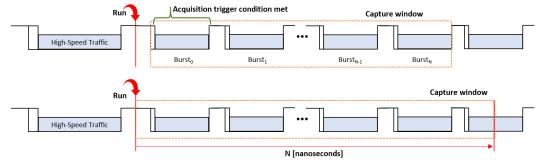

| Figure 7    | Illustration of two PHY-based acquisitions. Above, recording is triggered on first observed  |   |

| burst and   | depth is determined by user-defined N bursts. Below, acquisition begins immediately and      |   |

| depth is fo | or a user-defined period of N nanoseconds1                                                   | 0 |

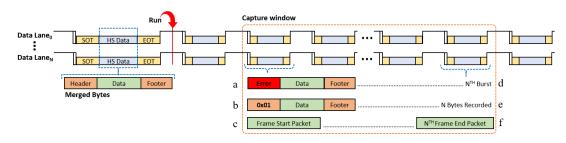

| Figure 8    | Illustration of three acquisitions triggered on merged high-speed traffic events: (a) header |   |

| error, (b)  | user-defined data type identifier and (c) frame start packet. Three methods of acquisition   |   |

| depth are   | shown: (d) user-defined N bursts, (e) bytes, and (f) frames.                                 | 0 |

| Figure 9    | Introspect ESP software environment, left, and right, examples of image captures1            | 1 |

| Figure 10   | SV3C MIPI D-PHY Analyzer connections1                                                        | 2 |

| Figure 11   | Illustration of the 240-pin SEARAY connector1                                                | 2 |

|             |                                                                                              |   |

## List of Tables

| Table 1 | Ordering part numbers for this product and related ones                                     | . 5 |

|---------|---------------------------------------------------------------------------------------------|-----|

| Table 2 | DPRX methods for triggering a D-PHY acquisition                                             | 10  |

| Table 3 | Units available for defining depth of an acquisition, accompanied with a user-defined value | 11  |

| Table 4 | Mapping of Lower MXP Connector (Lane Pinout)                                                | 13  |

| Table 5 | General Specifications                                                                      | 14  |

| Table 6 | Receiver Characteristics                                                                    | 15  |

| Table 7 | Clocking Characteristics                                                                    | 15  |

| Table 8 | Pattern and Protocol Handling Characteristics                                               | 16  |

| Table 9 | Physical Characteristics                                                                    | 17  |

### Introduction

#### **Overview**

The SV3C-DPRX D-PHY Analyzer is an ultra-portable, high-performance instrument for exercising and validating MIPI D-PHY transmitters as well as probing live MIPI D-PHY links. The Analyzer is data-rate agile, making it ideal for the capture and analysis of MIPI transmitters used in cameras, displays, and other devices. It also includes integrated LP and HS receivers, dynamic termination, and offers sophisticated capture, compare, and analysis modes.

The D-PHY Analyzer operates using the highly versatile Introspect ESP software environment that allows for automating transmitter tests such as CRC error counting or protocol timings.

This document includes electrical specifications of the Analyzer and provides details on the various methods for the capture and analysis of D-PHY traffic.

Please refer to the *Help Menu* within the Introspect ESP software for additional operating instructions.

#### **Key Benefits**

- Any-rate operation

- Flexible lane assignment

- Protocol Analyzer suite for CSI-2, DSI, and DSI-2

- Video frame extraction

- Precision time stamps to help understand each physical layer event

- Advanced triggering based on physical-layer or protocol-layer events

- Continuous monitoring mode for long-term error checking

- Programmable trigger I/O

- Intuitive state-of-the-art Python programming environment

- Reconfigurable, protocol customization (on request)

#### **Applications**

- Physical layer validation of MIPI D-PHY transmitters

- Protocol analysis for CSI-2, DSI, and DSI-2

- IP and software validation testing

- Debug of active D-PHY links

- Interface test

- Plug-and-play system-level validation

## **Ordering Information**

This product is part of the SV3C family of MIPI analyzer products. The following table describes the part numbers and key feature differentiators.

Table 1

Ordering part numbers for this product and related ones.

| Part Number | Name                                         | Key Differentiators       |

|-------------|----------------------------------------------|---------------------------|

| 4585        | SV3C-DPRX - SV3C D-PHY Analyzer Bundle (this | Covers the MIPI D-PHY     |

|             | product)                                     | physical layer            |

| 4590        | SV3C-DPRXCPRX - SV3C Combo C-PHY/D-PHY       | Combo D-PHY and C-PHY     |

|             | Analyzer Bundle                              | capability                |

| 4594        | SV3C DPRX Upgrade                            | Firmware and software     |

|             |                                              | license upgrade from 4585 |

|             |                                              | to 4590                   |

### Features

#### **Complete D-PHY Receiver Implementation**

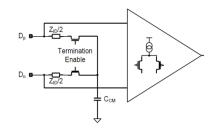

The SV3C DPRX is a complete, integrated, 4-lane D-PHY receiver providing the analog front-end circuitry for D-PHY as well as a complete protocol back-end. As shown in Figure 1, each lane contains low power (LP) threshold voltage detectors, dynamically controlled D-PHY termination resistors, and fully differential high speed (HS) receivers. The real-time behavior of the DPRX enables broad acquisition capabilities on physical-layer and protocol-layer events as detailed in Figure 2. The figure illustrates two common setups for deploying the DPRX, which can be used as either a terminating receiver or to probe live links.

Figure 1 SV3C receiver illustration showing automatic termination switches.

*Figure 2* (a) Illustration of the DPRX as a terminating end-point receiver, or (b) while probing a complete D-PHY link.

### **Protocol Analysis and Precision Time Stamps**

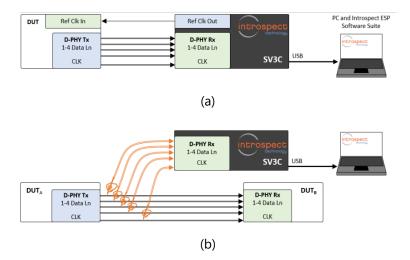

The SV3C DPRX is a complete protocol analyzer for both camera and display serial interfaces. Either protocol can be selected within a single session, and the analyzer automatically adjusts its viewer displays based on the protocol being measured (Figure 3). At the same time, irrespective of the protocol, five viewers provide insight into PHY and protocol events while hyperlinks make for quick and intuitive navigation across the layers, namely:

**HS Bursts** – View each high-speed burst, by lane, with quick statistics of the time of arrival in nanoseconds, SOT offset and captured bits in each

**CSI/DSI Packets** – Merged traffic from all lanes is shown as unique packets. Headers are decoded for easy, high-level viewing, and errors (CRC, ECC1, ECC2) are automatically highlighted

**LP States** – Each LP state is captured along with its time of arrival and duration; this viewer is extremely effective for building an visualization of the physical layer events

**Frame Viewer** – Images are automatically reconstructed, even if incomplete, with details such as pixel format, virtual channel, and image dimensions

Figure 3 Protocol analyzer views.

To enable the acquisition of high definition video streams under realistic traffic conditions, the SV3C DPRX relies on event-based captures, assigning a time stamp to each pertinent event of the physical layer and protocol layer. This allows for optimized data storage and extremely efficient long-term data analysis. In terms of display, each viewer contains a column dedicated to the precision time stamps of a given burst, packet, LP event or frame. Correlating events in time makes it easy to identify anomalous transitions, unexpected short- or long-packets, and other physical layer perturbations, as depicted in Figure 3.

### Hardware CRC Checking and Packet Error Rate Testing

Another fundamental feature of the SV3C-DPRX D-PHY Analyzer is hardwarebased packet error-rate detector. Similar to traditional BER, the PERT enables the measurement of real D-PHY transmissions from CSI generators or DSI generators. As illustrated in Figure 4, the Analyzer detects and filters all signal waveforms and compares only the packet data transmitted between SOT and EOT, registering errors after the data has been merged between lanes, thereby comparing errors in packets rather than bits.

Figure 4 Illustration of packet error rate testing.

### **Advanced Trigger Modes**

Figure 5 shows the user interface for defining the trigger mechanisms within the Analyzer. At the highest level, the Analyzer can be programmed to perform immediate captures (in which all data is measured irrespective of whether there are LP transitions or not) or burst-mode captures (Figure 6). The benefit of the immediate capture mode is that it allows for pattern learning and detecting multiple non-deterministic / non-repetitive packets. On the other hand, triggered captures offer a more focused view of D-PHY global timing parameters. In this mode, the D-PHY Analyzer sets the termination resistors into automatic mode. Then, the analyzer waits for a valid LP to HS entry sequence before enabling a capture. If no valid HS-entry transition is detected, the capture returns an empty array. However, when a valid HS-entry transition is detected, the capture starts immediately.

#### Introduction and Features

|                                                                             | (SV3C_4L3G_MIPI_DPHY_ANALYZER2)                                                                                   |                                                                          | >                                                                             |

|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| File Edit IESP/MIPI_DPHY_ANA                                                |                                                                                                                   |                                                                          |                                                                               |

| Params                                                                      | Log                                                                                                               | Results                                                                  |                                                                               |

| Components                                                                  | csiDataCaptur                                                                                                     | re1 properties (class: MpiDphyC                                          | siDataCapture)                                                                |

| csiDataCapture1<br>dphyDataCapture1<br>dsiDataCapture1<br>globalClockConfig | laneList<br>lanes<br>expectedPattern                                                                              | laneList 1<br>[1-4]                                                      |                                                                               |

| laneList1<br>pertMeasurement1                                               | captureMode<br>captureSize                                                                                        | burst 💻                                                                  |                                                                               |

| permeasurement                                                              | triggerCondition                                                                                                  | frameStart                                                               |                                                                               |

|                                                                             | dataTypeSequenceTrigger<br>lpSequenceTrigger<br>preTriggerDuration                                                | anyBurst<br>anyError<br>dataTypeSequen                                   | -                                                                             |

|                                                                             | post Tingger Duration<br>timeout<br>want Analysis<br>save Results                                                 | frameStart<br>headerError<br>immediate<br>ipSequence<br>payloadError     |                                                                               |

| Add Remove Config                                                           | triggerCondition<br>The "triggerCondition" specifies what will tr<br>"triggerCondition" is "immediate", the captu | igger the the data capture when<br>are will start immediately. If "trigg | the "captureMode" is "burst". If<br>erCondtion" is "anyBurst", the capture wi |

| Test Procedure                                                              |                                                                                                                   |                                                                          |                                                                               |

| 1 globalClockConfig.set<br>2 csiDataCapture1.run()                          |                                                                                                                   |                                                                          | Í                                                                             |

| 3 pertMeasurement1.run (<br>4<br>5                                          |                                                                                                                   |                                                                          | ,                                                                             |

Figure 5 Introspect ESP GUI for the SV3C DPRX. Top left: Components, shows CSI, DSI and PHY data acquisition methods. Top right: Properties, showing CSI Data capture. Bottom: test procedure ready to execute a CSI Data Capture, then PERT.

Triggered capture window

Figure 6 Illustration of multi-packet, per-lane PHY-level capture (Top), and triggered packet capture (Bottom).

Acquisitions and their depth are defined in time, by PHY events or by bytes of merged high-speed traffic. Figure 7 illustrates two methods of triggering acquisitions by PHY events. In Figure 7 (top), an acquisition begins on the first high-speed burst witnessed and completed after user-defined *N* bursts are recorded. In Figure 7 (bottom), a capture begins immediately and the Analyzer records for a user-defined period of *N* nanoseconds. Figure 8 illustrates three examples of triggering acquisitions on merged, high-speed data. The DPRX supports one to four data lanes and independently merges and monitors bytes. Acquisition start is user-defined as the first event observed: (a) error within a

Introduction and Features

Figure 7 Illustration of two PHY-based acquisitions. Above, recording is triggered on first observed burst and depth is determined by user-defined N bursts. Below, acquisition begins immediately and depth is for a user-defined period of N nanoseconds.

Figure 8 Illustration of three acquisitions triggered on merged high-speed traffic events: (a) header error, (b) user-defined data type identifier and (c) frame start packet. Three methods of acquisition depth are shown: (d) user-defined N bursts, (e) bytes, and (f) frames.

packet header, (b) variable data type identifier, here chosen as 0x01 and (c) frame start packet (CSI only). The depth of the acquisition for each is arbitrarily chosen according to the number of *N* received: (d) bursts, (e) bytes and (f) frame end packets. Finally, for completeness, Table 2 and Table 3 provide a list of trigger mechanism that are available in the Analyzer.

| triggerCondition  | Туре      | Trigger Description                                                                        |

|-------------------|-----------|--------------------------------------------------------------------------------------------|

| anyBurst          | РНҮ       | the first high-speed burst witnessed over any data or clock lane                           |

| immediate         | Time-base | time-base acquisition, beginning immediately when run                                      |

| lpSequence        | РНҮ       | user-defined sequence of LP states, e.g. "11,01,00" reflects a proper LP-HS entry sequence |

| anyError          | CSI, DSI  | the first error is registered: header, CRC or payload                                      |

| dataTypeSequence  | CSI, DSI  | user-defined integer value to be identified in a packet header                             |

| headerError       | CSI, DSI  | protocol layer, the first error recognized in a packet header                              |

| payloadError      | CSI, DSI  | protocol layer, the first error recognized in a packet payload                             |

| frameStart        | CSI       | CSI-only, any packet with header data type 0x00 indicating the beginning of a frame        |

| verticalSyncStart | DSI       | DSI-only, any packet with header data type 0x01 indicating the beginning of a frame        |

#### Table 2DPRX methods for triggering a D-PHY acquisition.

| Table 3 | Units available for defining depth o | of an acquisition, accompo | anied with a user-defined value. |

|---------|--------------------------------------|----------------------------|----------------------------------|

|---------|--------------------------------------|----------------------------|----------------------------------|

| postTriggerType            | Туре      | Description                                                          |

|----------------------------|-----------|----------------------------------------------------------------------|

| durationInNs               | Time-base | time-base acquisition, defined in nanoseconds                        |

| numberOfBursts             | РНҮ       | the total number of unique bursts acquired, across all data lanes    |

| numberOfBytes              | РНҮ       | the total number of bytes recorded between SOT and EOT of all bursts |

| numberOfLpCommands         | РНҮ       | the first error is registered: header, CRC or payload                |

| numberOfLpStates           | РНҮ       | number of unique LP states, e.g. "11,01,00" would be 3               |

| nuberOfFrameEnds           | CSI       | protocol layer, the number of frame-end packets recorded             |

| numberOfVerticalSyncStarts | DSI       | protocol layer, the number of packets with data type identifier 0x01 |

### **Automation**

The SV3C DPRX D-PHY Analyzer is operated using the award-winning Introspect ESP software, a Python-based scripting environment. Shown in Figure 9, it includes a comprehensive suite of components and methods for executing capture and analysis of D-PHY transmissions, and a canvas for automating test procedures and rich analysis. The Python library is open, and an optional .NET DLL library provides access for integration with DUTs, other test equipment using Python, or alternative programming languages.

*Figure 9* Introspect ESP software environment, left, and right, examples of image captures.

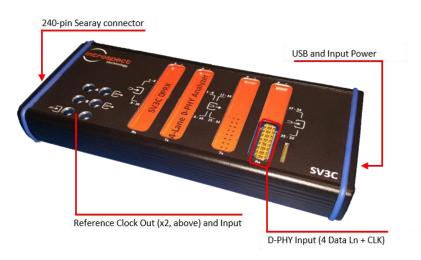

## Physical Description and Pinout

Figure 10 shows the physical connections of the SV3C MIPI D-PHY Analyzer. A single HUBER+SUHNER MXP connection provides input for the high-speed D-PHY lanes: four data lanes and one clock (MXP to SMA-Female breakout cable included). Differential SMP connections for reference clock output and input are available for synchronization with devices under test (DUT). A 240-pin SEARAY connection, depicted in Figure 11, provides programmable GPIO for various purposes such as:

- Low-speed communications with DUT via SPI or I2C

- Programmable trigger outputs based on real-time events such as errors, bursts or received data patterns

- Trigger input for data acquisition

Finally, Table 4 shows the pin mapping on the MXP connector.

Figure 10 SV3C MIPI D-PHY Analyzer connections.

*Figure 11* Illustration of the 240-pin SEARAY connector.

| ~                    | Connector Pin Number | Corresponding RX Lane |

|----------------------|----------------------|-----------------------|

| 1 9<br>2 10          | 1,2                  | Lane 1 (P,N)          |

| 2 10<br>3 11<br>4 12 | 3,4                  | Lane 2 (P,N)          |

| 4 12<br>5 13<br>6 14 | 5,6                  | Lane 3 (P,N)          |

| 7 15<br>8 16         | 9,10                 | Lane 4 (P,N)          |

| 0 8                  | 13, 14               | CLK (P,N)             |

Table 4 Mapping of Lower MXP Connector (Lane Pinout).

## Specifications

#### Table 5 General Specifications

| Value            | Units                                                                                                                                                                      | Description and Conditions                                                                                                                                                                                   |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                                                                                                                                                            |                                                                                                                                                                                                              |

| D-PHY            |                                                                                                                                                                            | Version 1.2, 2.0                                                                                                                                                                                             |

| CSI-2            |                                                                                                                                                                            | Version 1.3, 2.0                                                                                                                                                                                             |

| DSI              |                                                                                                                                                                            | Version 1.3                                                                                                                                                                                                  |

| DSI-2            |                                                                                                                                                                            | Version 1.0                                                                                                                                                                                                  |

|                  |                                                                                                                                                                            |                                                                                                                                                                                                              |

| -                |                                                                                                                                                                            | Version 1.2                                                                                                                                                                                                  |

|                  |                                                                                                                                                                            | Tester automatically detects LP and HS data                                                                                                                                                                  |

| ,                |                                                                                                                                                                            | Acquire transitions only between LP wire states                                                                                                                                                              |

| HS Only          |                                                                                                                                                                            | Continuous, high-speed only acquisition                                                                                                                                                                      |

|                  |                                                                                                                                                                            |                                                                                                                                                                                                              |

| 4 Data + 1 Clock |                                                                                                                                                                            |                                                                                                                                                                                                              |

| 2                |                                                                                                                                                                            | Separate clock for providing reference to the DUT                                                                                                                                                            |

| 1                |                                                                                                                                                                            | Used as external Reference Clock input                                                                                                                                                                       |

| 3                |                                                                                                                                                                            | Armed in software to trigger the start of specific                                                                                                                                                           |

|                  |                                                                                                                                                                            | measurements                                                                                                                                                                                                 |

| 3                |                                                                                                                                                                            | Armed in software to flag test completion or pass/fail                                                                                                                                                       |

|                  |                                                                                                                                                                            | criteria                                                                                                                                                                                                     |

|                  |                                                                                                                                                                            |                                                                                                                                                                                                              |

| 80               | Mbps                                                                                                                                                                       |                                                                                                                                                                                                              |

| 3                | Gbps                                                                                                                                                                       |                                                                                                                                                                                                              |

| 10               | MHz                                                                                                                                                                        |                                                                                                                                                                                                              |

|                  |                                                                                                                                                                            |                                                                                                                                                                                                              |

| 250              | MHz                                                                                                                                                                        |                                                                                                                                                                                                              |

|                  |                                                                                                                                                                            |                                                                                                                                                                                                              |

| 10               | MHz                                                                                                                                                                        |                                                                                                                                                                                                              |

| 250              | MHz                                                                                                                                                                        |                                                                                                                                                                                                              |

| 1                | kHz                                                                                                                                                                        |                                                                                                                                                                                                              |

|                  |                                                                                                                                                                            | Support for LVDS, LVPECL, CML, HCSL, and CMOS.                                                                                                                                                               |

|                  |                                                                                                                                                                            |                                                                                                                                                                                                              |

| 25               | ns                                                                                                                                                                         |                                                                                                                                                                                                              |

| -                | D-PHY<br>CSI-2<br>DSI<br>DSI-2<br>Custom<br>VESA<br>Automatic<br>LP Only<br>HS Only<br>4 Data + 1 Clock<br>2<br>1<br>3<br>3<br>3<br>80<br>3<br>10<br>250<br>10<br>250<br>1 | D-PHY<br>CSI-2<br>DSI<br>DSI-2<br>Custom<br>VESA<br>Automatic<br>LP Only<br>HS Only<br>4 Data + 1 Clock<br>2<br>1<br>3<br>3<br>3<br>80<br>Mbps<br>Gbps<br>MHz<br>250<br>MHz<br>10<br>MHz<br>250<br>MHz<br>Hz |

#### Table 6 Receiver Characteristics

| Parameter                                        | Value                                         | Units | Description and Conditions |

|--------------------------------------------------|-----------------------------------------------|-------|----------------------------|

| Input Coupling                                   |                                               |       |                            |

| Input Impedance                                  | 50                                            | Ω     |                            |

|                                                  | Hi-Z                                          | Ω     |                            |

| HS Performance                                   |                                               |       |                            |

| Minimum Detectable Differential<br>Voltage       | 90                                            | mV    |                            |

| Maximum Allowable Differential<br>Voltage        | 600                                           | mV    |                            |

| <b>Resolution Enhancement &amp; Equalization</b> |                                               |       |                            |

| Minimum DC Gain                                  | 0                                             | dB    |                            |

| Maximum DC Gain                                  | 8                                             | dB    |                            |

| DC Gain Control                                  | Per-receiver                                  |       |                            |

| Equalization Control                             | Per-receiver                                  |       |                            |

| Timing Generator Performance                     |                                               |       |                            |

| Resolution at Maximum Data Rate                  | 7.8125                                        | mUI   |                            |

| Differential Non-Linearity Error                 | +/- 0.5                                       | LSB   |                            |

| Integral Non-Linearity Error                     | +/- 5                                         | ps    |                            |

| Range                                            | +/- 2                                         | UI    |                            |

| LP Voltage Threshold Controls                    |                                               |       |                            |

| Minimum Programmable Threshold<br>Voltage        | -100                                          | mV    |                            |

| Maximum Programmable Threshold<br>Voltage        | 1500                                          | mV    |                            |

| Threshold Voltage Resolution                     | 1                                             | mV    |                            |

| Threshold Voltage Accuracy                       | Larger of 5.0 mV<br>or 2.0 % of<br>programmed |       |                            |

|                                                  | value                                         |       |                            |

#### Table 7 Clocking Characteristics

| Parameter                                       | Value | Units | Description and Conditions |

|-------------------------------------------------|-------|-------|----------------------------|

| Internal Time Base                              |       |       |                            |

| Number of Internal Frequency<br>References      | 1     |       |                            |

| Frequency Resolution of<br>Programmed Data Rate | 1     | Kbps  |                            |

| Parameter                           | Value               | Units | Description and Conditions                                     |

|-------------------------------------|---------------------|-------|----------------------------------------------------------------|

| Preset Patterns                     |                     |       |                                                                |

| Standard Built-In Patterns          | All Zeros           |       |                                                                |

|                                     | D21.5               |       |                                                                |

|                                     | K28.5               |       |                                                                |

|                                     | K28.7               |       |                                                                |

|                                     | DIV.16              |       |                                                                |

|                                     | DIV.20              |       |                                                                |

|                                     | DIV.40              |       |                                                                |

|                                     | DIV.50              |       |                                                                |

|                                     | PRBS.5              |       |                                                                |

|                                     | PRBS.7              |       |                                                                |

|                                     | PRBS.9              |       |                                                                |

|                                     | PRBS.11             |       |                                                                |

|                                     | PRBS.13             |       |                                                                |

|                                     | PRBS.15             |       |                                                                |

|                                     | PRBS.18             |       |                                                                |

|                                     | PRBS.23             |       |                                                                |

|                                     | PRBS.31             |       |                                                                |

| User-programmable Pattern Memory    |                     |       |                                                                |

| Individual Expected Pattern         | Per-lane            |       |                                                                |

| Minimum Pattern Segment Size        | 8                   | bits  |                                                                |

| Total Memory Space for              | 4G                  | Bytes |                                                                |

| Expected Patterns                   |                     | ,     |                                                                |

| BERT Characteristics                |                     |       |                                                                |

| Maximum Packet Size                 | 2 <sup>32</sup> - 1 |       |                                                                |

| Maximum Number of Packets           | 2 <sup>32</sup> - 1 |       |                                                                |

|                                     |                     |       |                                                                |

| Maximum Number of Repeats           | 2 <sup>32</sup> - 1 |       |                                                                |

| Maximum Time Between SOT in         | 1                   | ms    |                                                                |

| Burst Mode                          |                     |       |                                                                |

|                                     |                     |       |                                                                |

| Minimum Time Between SOT in         | TBD                 | UI    |                                                                |

| Burst Mode                          |                     |       |                                                                |

| Capture Memory Depth                | 4G                  | Bytes |                                                                |

| Additional Protocol Characteristics |                     |       |                                                                |

|                                     |                     |       |                                                                |

| Escape Mode Command                 | Per Lane            |       |                                                                |

| Detection                           | Auto rosponse       |       | Automatically respond to Scrembling Mode Commend               |

| De-scrambling                       | Auto response       |       | Automatically respond to Scrambling Mode Command (0x27) packet |

|                                     | Manual override     |       | Manually disable scrambling through software                   |

| Decompression                       | Auto PPS            |       | Automatically receive PPS table from transmitter               |

|                                     | Set PPS             |       | Program the PPS table in software                              |

|                                     | 500115              |       |                                                                |

#### Table 8 Pattern and Protocol Handling Characteristics

#### Table 9 Physical Characteristics

| Parameter              | Value                | Units   | Description and Conditions               |

|------------------------|----------------------|---------|------------------------------------------|

| Dimensions             |                      |         |                                          |

| Length                 | 9.50, 241.30         | in, mm  |                                          |

| Width                  | 4.25, 107.95         | in, mm  |                                          |

| Height                 | 1.30, 33.30          | in, mm  |                                          |

| Weight                 | 2                    | lb      |                                          |

| Physical Connections   |                      |         |                                          |

| D-PHY Rx               | Huber & Suhner 16-   | pin MXP |                                          |

| GPIO                   | Samtec SEARAY        |         | PN CON-SAMTEC-SEAF-40-01-L-06-2-RA-LP-TR |

| Ref Clock In           | SMP Differential Pai | ir      |                                          |

| Ref Clock Out          | SMP Differential Pai | ir      |                                          |

| PC Connection          | USB                  |         |                                          |

| Power Switch/Connector | AC adapter provided  | b       | 110/220 V, 50/60 Hz                      |

| Energy Use             |                      |         |                                          |

| Power Dissipation      | < 60                 | W       |                                          |

| Revision Number | History                      | Date            |

|-----------------|------------------------------|-----------------|

| 1.0             | Import from CPRX v1.1.       | June 7, 2014    |

| 1.1             | Updated document template.   | June 3, 2015    |

| 1.2             | Updates to Protocol Analyzer | July 6, 2017    |

| 1.3             | Updates to text              | August 24, 2017 |

The information in this document is subject to change without notice and should not be construed as a commitment by Introspect Technology. While reasonable precautions have been taken, Introspect Technology assumes no responsibility for any errors that may appear in this document.

© Introspect Technology, 2017 Published on August 24, 2017 EN-D004E-E-17187